SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

Exclusive supplier of xSPI memory controller IP for the Critical Link LLC (CL) MitySOM-C10L Development Kit and SOM

The MitySOM-C10L products have an Intel Cyclone 10 FPGA and an xSPI x8 200 MHz PSRAM memory

CL customers can expect fast project starts. SLL’s memory controller IP and reference designs are specifically targeted to the MitySOM-C10L.

Customers purchase the MitySOM-C10L development kit from CL or from CL distribution sales partners. Customers then register their Kit and request SLL’s xSPI memory controller IP on this website. The registration link is at the bottom of this webpage.

Introduction to SLL’s xSPI memory controller (SLL-CL-MBMC) for MitySOM-C10L products

SLL’s SLL-CL-MBMC IP exclusively supports Critical Link (CL) MitySOM-C10L Development Kits and System on Modules (SoM). These CL products have an xSPI memory and an Intel Cyclone 10 LP FPGA supporting the Nios® II and Nios® V ecosystems.

SLL is the sole authorised supplier of xSPI memory controller IP for Critical Link.

SLL-CL-MBMC is a version of SLL’s widely used xSPI Multiple Bus Memory Controller (MBMC IP v3.2.x).

- This exclusive version of SLL’s IP is called SLL-CL-MBMC v3.2.x.

- It is available in R&D and Production versions.

- It is provided with reference designs for the MitySOM Development Kit with AP Memory PSRAM for use with Nios® II and Nios® V ecosystems.

Verified Critical Link MitySOM-C10L customers can register their Kit and request R&D and Production licenses of SLL-CL-MBMC IP at no cost. The registration link is at the bottom of this webpage.

Supported Critical Link Products and Data Sheets

- The upgradeable MitySOM-C10L System on Module (SoM) with low power Cyclone 10L FPGA and x8 xSPI PSRAM – ( MITYSOM C10L-7Q-3X3-RI ).

https://www.criticallink.com/product/mitysom-c10l/

https://www.criticallink.com/wp-content/uploads/MitySOMC10L-Datasheet.pdf - The MitySOM-C10L Development Kit – https://www.criticallink.com/product/mitysom-c10l-development-kit

- MITYSOM Development KIT, containing PCA, MitySOM-C10L Dev Board, P/N 80-001651

The MitySOM-C10L Development Kit is a good replacement for the original Intel C10L Evaluation Kit.

- SLL was also the sole official supplier to Intel for the xSPI memory controller for Intel’s C10L Evaluation Kit. It was promoted globally by Intel and Intel channel partners.

- SLL can support Intel customers migrating from an Intel C10LP Eval Kit to the new MitySOM-C10L Eval Kit.

- Critical Link and SLL are both Intel Gold Partners.

How To Buy MitySOM Products

Sales enquiries and purchases can be made to Critical Link

- Critical Link LLC Website

- Phone: (315) 425-4045

- Email: sales@criticallink.com

Also to CL’s official distribution partners:

SLL is also a direct partner with several of these major distribution companies.

- SLL works with their FAE to support their customers. SLL also assists their FAE to make reference designs that employ SLL’s IP’s.

- One example is the Arrow reference design. This employs SLL’s memory controller IP on Critical Link’s MitySOM-C10L.

- MitySOM customers can also ask their FAE to connect with SLL

A fast, low power xSPI PSRAM on MitySOM-C10L products

- It is the x8 200 MHz Xccela PSRAM from AP Memory

- AP Memory is a world leading manufacturer of Pseudo-SRAM (PSRAM xSPI memory) since 2011.

- AP Memory PSRAM shipment volume by 2021 already exceeded 6 billion units.

- SLL’s xSPI SLL-CL-MBMC memory controller IP specifically supports the AP Memory xSPI PSRAM memory device on the Critical Link MitySOM-C10L Development Kit and SOM.

- SLL is the official xSPI memory controller IP partner of most xSPI memory manufacturers, including AP Memory.

- Major xSPI memory manufacturers including AP Memory and SLL are Members of the Micron founded Xccela Consortium.

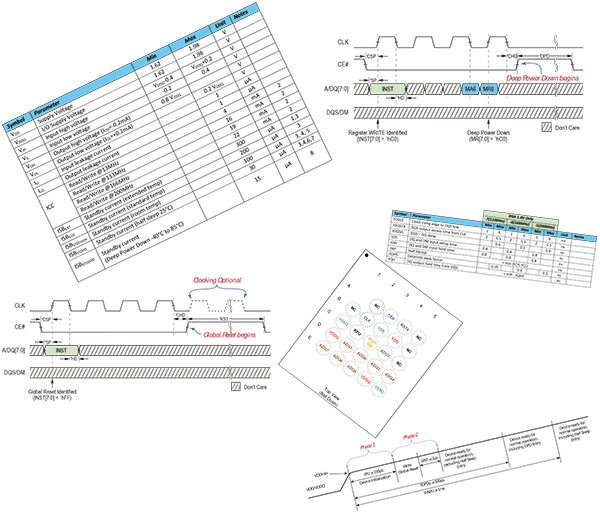

- The Xccela Bus is one of the several similar xSPI memory bus protocols supported by SLL’s Multiple Bus Memory Controller (MBMC) IP, including HyperBus, OctaBus, Xccela Bus, and others.

About Critical Link MitySOM-C10L

The MitySOM-C10L series are highly configurable, small form-factor System-on-Modules. They feature an Intel / Altera Cyclone 10 LP (Low Power) field programmable gate array (FPGA) and include on-board power supplies, NOR FLASH and an AP Memory Xccela PSRAM memory subsystems.

Specifications:

- CYCLONE 10 LP FPGA – U484 PACKAGE

- Up To 80K Logic Elements (LE)

- 4 Phase Locked Loops (PLLs)

- Up to 500Mhz Global Clock

- Up To 2.7Mb Embedded Memory

- Up To 244 DSP Blocks

- Up To 6 FPGA PLLs

- Single Event Upset (SEU) detection

- MEMORY

- Up To 32 Mbyte (256 Mbit) HyperRAM at 200 MB

- Up To 32 Mbyte (256 Mbit) QPSI NOR FLASH

- INTEGRATED POWER MANAGEMENT

- Single +5V Input for on-board needs

- User defined Bank IO Voltage

- MECHANICAL

- 260-Pin Card Edge Connector

- Small 70mm (2.75”) x 30mm (1.2”) size

- ADDITIONAL DETAILS

- JTAG Interface Available on Edge Connector

- On-Board 50 MHz clock

- Configuration Status and General-Purpose Tri-Color LEDs

Fast MitySOM-C10L project starts with SLL’s xSPI memory controller SLL-CL-MBMC

SLL’s Multiple Bus Memory Controller for Critical Link (SLL-CL-MBMC v3.2.x) supports the AP Memory x8 200 MHz PSRAM that is surface mounted on the following MitySOM product order codes:

- MITYSOM C10L-7Q-3X3-RI

- MITYSOM Development KIT, containing PCA, MitySOM-C10L Dev Board, P/N 80-001651

SLL-CL-MBMC is specifically designed to simplify customer uptake for fast project starts, even by designers who have never used xSPI memories before.

- The capabilities immediately available in SLL-CL-MBMC IP are expected to be suitable for most customer’s proprietary base boards using supported MitySOM.

Any MitySOM customers that need different capabilities than those available immediately in the SLL-CL-MBMC IP can contact info@synaptic-labs.com with your specific requirements. For example,

- If MitySOM customers require more than 150 MHz or x16 or dual channel; or

- If MitySOM customers want to surface mount any other additional xSPI memory device variant/s on their proprietary base-board connected to a supported CL MitySOM. You can select from the wide range of supported HyperBus, OctaBus, OctalBus or other Xccela Bus xSPI memory devices from up to 9 memory manufacturers including Everspin STT-MRAM.

Information about more capabilities can be found on SLL’s xSPI MBMC IP v.3.3.x product page.

- Visit our Customers webpage to see some examples of SLL memory controller customers around the globe and to see some examples of their many use cases and applications since 2016.

SLL-CL-MBMC v3.2.x Capabilities (other capabilities can be requested)

- Includes tight integration with Intel’s Platform Designer graphical system integration tool

- A simplified GUI user-interface to make adoption of the IP very easy in customer projects

- A maximum memory channel clock speed of 150 MHz DDR. This enables easy place-route and static timing sign off, even in complex customer designs.

- A maximum burst length of 32-bytes. This is usually enough to support efficient software performance.

- Features a high quality local interconnect, with support for the following interconnect protocols:

- Intel Avalon-MM protocol

- other interconnect protocols available on request…

- Includes internal clock-crossing circuitry between the local bus interconnect and the external memory channel. This reduces circuit area and improves the performance of the customer’s design

- Excellent memory access performance for both latency sensitive and bandwidth intensive applications:

- The round trip time for read memory transfer requests through the memory controller has been optimized for latency sensitive applications, such as processor cores.

- Note: SLL offers a range of cache technologies to significantly increase the performance of processor cores that do not have internal instruction and/or data caches when accessing external memories.

- Send your enquiry to info@synaptic-labs.com

- Features low circuit area and low SRAM usages, making SLL’s memory controller viable for use in resource constrained designs.

- Supports x8 data path width in a single instantiation of SLL’s memory controller IP

- Supports 1 instantiation of the memory controller IP accessing the surface mounted AP Memory PSRAM

- Please contact SLL at info@synaptic-labs.com if you require 2 or more instantiations of our memory controller IP in your Quartus project.

Remember: MitySOM customers that need any more capabilities in the SLL-CL-MBMC IP can contact info@synaptic-labs.com with your requirements.

Support for the Nios® V ecosystem on MitySOM-C10L

To quote the Intel website: ”Nios® V processor is the next generation of soft processor for Intel® FPGAs based on the open-source RISC-V Instruction Set Architecture.”

SLL-CL-MBMC reference designs are already available for the Nios® V ecosystem.

Note 1. Intel has not yet released Nios® V with cache. Intel is still updating the Nios® V support documentation.

Note 2. MitySOM-C10L customers that are early adopters of the Nios® V ecosystem may need to purchase some technical support hours from SLL to help implement their designs.

A calculator for estimating the effective bandwidth of the AP Memory PSRAM with SLL IP

For all DDRx SDRAM, and PSRAM devices, the effective memory bandwidth is always less than the wire speed. The effective memory bandwidth of your application using PSRAM devices depends on:

- The data path width of the memory channel (x8, x16, ..)

- The memory channel clock speed (ideally the highest speed supported by the memory device and SLL’s memory controller IP for that FPGA device family)

- The initial access latency (ideally the lowest value permitted by the PSRAM device for a given clock speed)

- The burst length of memory transfer requests issued to SLL’s memory controller IP (ideally 64 bytes or higher to PSRAM)

- The number of concurrently outstanding memory transfer requests issued to SLL’s memory controller IP (ideally 2)

- With all types of PSRAM devices, the temperature grade of the memory device impacts the maximum burst length of PSRAM devices.

- The choice of x8 Xccela PSRAM protocol does not have a significant impact on performance.

As a starting point, you can use SLL’s estimated effective bandwidth calculator below. It will help you to find the optimal burst length(s) for your application’s use-case when using SLL’s memory controller with a specific Xccela PSRAM device variant. {The calculator is only a guide and actual results in your hardware may be different. For more information contact SLL at info@synaptic-labs.com }

How to start using SLL-CL-MBMC with your MitySOMC10L Development Kit

- Verified Critical Link MitySOM-C10L customers can request R&D and Production licenses of SLL-CL-MBMC IP at no cost. See the registration link below.

- Before manufacturing your own prototypes, please validate your pin-mapping and PCB layout with Synaptic Laboratories at info@synaptic-labs.com . This will reduce design risks.

- SLL is the domain expert for xSPI memories. We have supported Fortune Global 500’s down to SME’s around the globe to achieve project success in many applications using xSPI memories.

- You are invited to contact SLL at info@synaptic-labs.com to explore your project design and objectives using any xSPI memories with any specific FPGA family.